DOI: 10.5335/rbca.v17i1.16019

Vol. 17, N<sup>0</sup> 1, pp. 1−11

Homepage: seer.upf.br/index.php/rbca/index

#### ARTIGO ORIGINAL

# Estudo comparativo entre implementações neuromórficas utilizando Redes Neurais Pulsantes conectadas por Redes-em-Chip

# Comparative study between neuromorphic implementations using Spiking Neural Network connected by Network-on-Chip

Victor Benvenutti Cavalheiro <sup>[0,1]</sup>, Beatriz Oliveira Câmara <sup>[0,2]</sup>, Janaina Gonçalves Guimarães <sup>[0,3]</sup>

$^{1,3} Universidade \ Federal \ de \ Santa \ Catarina, \ ^2 Universidade \ de \ Brasília$  victorcava.ufsc@gmail.com; bia.camara@gmail.com; janaina.guimaraes@ufsc.br;

Recebido: 01/07/2024. Revisado: 08/03/2025. Aceito: 30/04/2025.

#### Resumo

A implementação eficiente de redes neurais em hardware, especialmente usando redes-em-chip para interconexão de redes neurais pulsantes em chips neuromórficos, é um avanço significativo em sistemas computacionais que imitam o cérebro humano. Este estudo realiza uma revisão sistemática sobre a integração dessas tecnologias em chips neuromórficos, usando a metodologia PRISMA para analisar diversos estudos e comparar diferentes abordagens em hardware. Os resultados destacam a importância de soluções eficientes em energia e desempenho para inteligência artificial. Apesar dos desafios técnicos, a computação neuromórfica está evoluindo rapidamente, com potencial para impulsionar várias tecnologias emergentes. Os desafios incluem explorar modelos de neurônios, técnicas de aprendizagem e estratégias de interconexão e roteamento para melhorar a eficiência e desempenho.

Palavras-Chave: Chips Neuromórficos; Hardware; PRISMA; Redes Neurais Pulsantes; Redes-em-Chip.

#### **Abstract**

The efficient implementation of neural networks in hardware, especially using networks-on-chip for the interconnection of spiking neural networks in neuromorphic chips, is a significant advancement in computational systems that mimic the human brain. This study conducts a systematic review on the integration of these technologies in neuromorphic chips, using the PRISMA methodology to analyze various studies and compare different hardware approaches. The results highlight the importance of energy-efficient and high-performance solutions for artificial intelligence. Despite technical challenges, neuromorphic computing is rapidly evolving, with the potential to advance several emerging technologies. The challenges include exploring neuron models, learning techniques, and interconnection and routing strategies to improve efficiency and performance.

Keywords: Hardware; Network-on-Chip; Neuromorphic Chips; PRISMA; Spiking Neural Networks.

# 1 Introdução

A aspiração de criar máquinas com capacidade de processamento superior à humana impulsiona a computação há décadas. A arquitetura de von Neumann, embora dominante, apresenta disparidades notáveis em comparação com o cérebro humano em termos de estrutura, eficiência energética e capacidades de processamento, levantando questões sobre alternativas inspiradas no cérebro (Schuman et al., 2017).

A computação neuromórfica, introduzida por Carver Mead em 1990 (Mead, 1990), utiliza componentes analógicos em Very-Large-Scale Integration (VLSI) para emular funções neurais biológicas eficientemente. Essa abordagem permite a criação de circuitos adaptativos com baixo consumo de energia, valiosos para robótica avançada e sistemas complexos de IA (Schuman et al., 2017).

Redes Neurais Pulsantes (SNN), interconectadas por Redes-em-Chip (NoC), são promissoras na computação neuromórfica. Simular numerosas sinapses, semelhante ao cérebro humano, exige sistemas de interconexão robustos e eficientes, o que torna as NoCs essenciais. Elas suportam a dinâmica adaptativa das SNNs, importante para aprendizado e adaptação (Basu et al., 2022). A combinação de NoCs e SNNs permite a simulação eficiente de processos cognitivos complexos, aumentando a eficiência e adaptabilidade dos sistemas de inteligência artificial (IA) (Walter et al., 2015). Essas tecnologias podem superar a eficiência energética e capacidade do cérebro humano, impactando neurociência, robótica e medicina (Lobo et al., 2020).

Diversas inovações na implementação desses chips evidenciam avanços significativos na computação neuromórfica. Por exemplo, a arquitetura H-NoC, proposta por Carrillo et al. (2012), adota uma organização hierárquica que distribui os neurônios em múltiplos níveis e incorpora técnicas de compressão de tráfego para otimizar a comunicação e a escalabilidade. Em paralelo, o DHyANA, desenvolvido por Holanda et al. (2016), utiliza uma abordagem digital que integra modelos de neurônios com estratégias de roteamento eficientes, demonstrando um equilíbrio promissor entre área, desempenho e consumo de energia.

Duas revisões importantes encontradas na literatura estrangeira serviram como base para este trabalho. Chen et al. (2022) exploraram diferentes abordagens para a implementação de SNNs, comparando arquiteturas analógicas, digitais e híbridas, além de discutir o uso de computação estocástica para otimizar a eficiência energética. Por outro lado, Basu et al. (2022) investigaram a escalabilidade de designs multi-core, destacando os desafios da interconexão entre chips e apresentando tabelas comparativas entre diversas arquiteturas neuromórficas.

Entretanto, a maior parte dessas revisões está disponível apenas em outros idiomas, o que dificulta o acesso e a disseminação do conhecimento para a comunidade de língua portuguesa. Diante disso, este trabalho busca preencher essa lacuna ao consolidar e contextualizar os avancos já alcançados, tornando esses conhecimentos mais acessíveis para pesquisadores da área.

Além disso, este estudo se diferencia das revisões anteriores ao realizar uma análise comparativa dos principais parâmetros que impactam o desempenho das implemen-

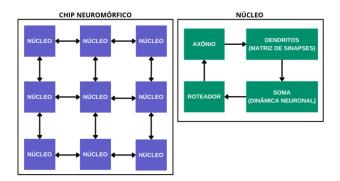

**Figura 1:** Arquitetura genérica de um chip neuromórfico e seus núcleos

tações neuromórficas de SNNs interconectadas por NoCs, como: modelos neuronais, mecanismos de aprendizagem, topologias, tecnologia de fabricação, consumo de energia e área de chip. buscando-se encontrar suas correlações. Essa abordagem permite encontrar correlações entre os paramêtros, além dos, pontos fortes e limitações de cada estratégia. E ainda, aponta direções futuras para o desenvolvimento tecnológico, contribuindo para a evolução da computação neuromórfica, especialmente no contexto nacional.

# Fundamentação Teórica

A estrutura de um chip neuromórfico é projetada para imitar a organização e o funcionamento do cérebro humano, promovendo alta eficiência energética e processamento paralelo. A Figura 1 ilustra um chip neuromórfico composto por múltiplos núcleos interconectados, cada um com sua própria funcionalidade específica. Cada núcleo inclui componentes importantes como o axônio, dendrito e soma, que são análogos aos componentes biológicos dos neurônios. O dendrito contém a memória sináptica e os elementos de integração, onde as entradas são somadas e processadas. O soma, responsável pela dinâmica neuronal, integra esses sinais e decide se um pico deve ser gerado. O axônio então transmite esses picos para outros núcleos através de um roteador (Basu et al., 2022).

Três características fundamentais definem os chips neuromórficos e servem de base para este estudo: o processamento que emula o comportamento neuronal, a arquitetura de comunicação utilizada para a interconexão dos neurônios e a forma como esses circuitos são impressos no chip. Essas características serão exploradas nos parágrafos subsequentes.

O roteador desempenha um papel fundamental no gerenciamento da comunicação tanto dentro do chip quanto entre chips diferentes. Esta arquitetura descentralizada permite que cada núcleo opere de forma independente, mas também compartilhe dados e se sincronize periodicamente, formando um fluxo de dados distribuído. A interconexão de múltiplos núcleos através de roteadores descentralizados garante escalabilidade, essencial para simulações em larga escala de redes neurais. Além disso, a utilização de roteadores de alta largura de banda é crítica para

superar os gargalos de desempenho causados pela comunicação em distâncias maiores dentro e entre chips. Essa abordagem modular e escalável torna os chips neuromórficos ideais para aplicações que requerem processamento em tempo real e alta eficiência energética, como inteligência artificial, robótica e sistemas embarcados (Basu et al., 2022). Em vista disso, as SNNs e NoCs são utilizadas para construir a estrutura em hardware.

As SNNs utilizam sinais elétricos discretos conhecidos como pulsos ou spikes para a comunicação entre neurônios, o que permite uma eficiência energética consideravelmente maior e uma capacidade de processamento mais alinhada com o funcionamento do cérebro humano (Lobo et al., 2020). Entre os modelos de neurônios pulsantes mais comuns, destacam-se o modelo Integrate-and-Fire (IF) e suas variantes como o Leaky Integrate-and-Fire (LIF), que incorporam a característica de vazamento para simular a perda gradual do potencial de membrana. O modelo de Hodgkin-Huxley (H-H), apesar de ser mais complexo e computacionalmente intensivo, oferece uma descrição detalhada da dinâmica iônica através da membrana neuronal. Já o modelo de Izhikevich (IZHI) combina a simplicidade do modelo IF com a precisão do modelo H-H, permitindo a simulação de diversos padrões de disparo neuronal com eficiência computacional (Yamazaki et al., 2022).

As NoCs são uma arquitetura de comunicação que utiliza conceitos de redes de computadores aplicados a sistemas em chip, proporcionando uma infraestrutura escalável e eficiente para a interconexão de múltiplos componentes dentro de um único chip (Alimi et al., 2021). A topologia de malha é uma das mais populares em NoCs, caracterizada por uma grade regular onde cada nó se conecta aos seus vizinhos cardinais, facilitando o roteamento simples e eficiente com latência previsível (Kundu e Chattopadhyay, 2014). Além da malha, existem outras topologias como torus, estrela, anel e árvore, cada uma com suas próprias vantagens e desvantagens em termos de latência, largura de banda e consumo de energia. As topologias híbridas combinam elementos dessas estruturas regulares para otimizar a comunicação, melhorando a largura de banda e o throughput global da rede (Ahmad e Sethi, 2020).

A tecnologia CMOS está amplamente presente nesses chips. Ela revolucionou a microeletrônica com sua capacidade de integrar componentes em um único chip, promovendo eficiência energética e alta resistência a interferências. Esta tecnologia facilita a criação de sistemas complexos e operacionais em espaços físicos reduzidos, integrando um amplo espectro de componentes (Jaeger e Blalock, 2015). A construção desses chips pode ser feita utilizando circuitos digitais e analógicos. Os principais exemplos encontrados na literatura são:

- · BrainScaleS: implementação analógica que utiliza tecnologia CMOS de 180 nm e incorpora 512 neurônios do tipo IF exponencial, e permite modelar redes complexas com mais de 10.000 sinapses por neurônio (Schemmel et al., 2010);

- Loihi: implementação digital da Intel fabricada em 14 nm, que integra 128 núcleos neuromórficos e três núcleos x86, permitindo simulações eficientes com 23,6 pJ por operação sináptica e escalabilidade para até 4096

- núcleos por chip (Davies et al., 2018);

- Neurogrid: implementação analógica que simula um milhão de neurônios em 16 Neurocores, permitindo o roteamento de pulsos a uma taxa de pico de 91 milhões por segundo, e é usada para computações matemáticas e algoritmos de controle em dispositivos de baixo consumo (Choudhary et al., 2012);

- TrueNorth: implementação digital da IBM que opera com 4096 núcleos neurosinápticos para simular 1 milhão de neurônios e 256 milhões de sinapses com um consumo de apenas 65 mW, e utiliza a topologia de Malha 2D (Akopyan et al., 2015).

As características descritas nesta seção serão fundamentais para a metodologia deste estudo, servindo como critérios para a seleção dos artigos analisados na próxima seção.

# Metodologia

Este estudo realizou uma revisão sistemática transversal seguindo as diretrizes do PRISMA (Preferred Reporting Items for Systematic Reviews and Meta-Analyses), reconhecidas por promover a transparência e qualidade em revisões sistemáticas e meta-análises (Moher et al., 2009).

O foco principal foi explorar e responder às perguntas:

- Como as implementações de chips neuromórficos com SNNs interligadas por NoCs se distinguem em modelos neurais, regras de aprendizagem, tecnologias de fabricação, tipos de circuitos e configurações topológicas?

- Como essas características contribuem para vantagens competitivas em desenvolvimento e desempenho:

- Quais são as tendências emergentes e desafios na literatura recente sobre essas implementações?

#### 3.1 Critérios de Seleção e Triagem dos Artigos

Os artigos deveriam focar na implementação de chips neuromórficos com SNNs interconectadas por NoCs, com acesso completo ao texto, publicados em inglês nos últimos quatorze anos. A coleta de dados ocorreu em março de 2024, utilizando a expressão de busca: (*network-on-chip*) AND (chip) AND (spiking neuron) AND (area) AND (power) AND (learning) AND (topology).

A seleção dos estudos, a avaliação da qualidade, a extração de dados e a análise dos resultados foram conduzidas conjuntamente por três avaliadores. As decisões foram tomadas por consenso, após discussões detalhadas sobre cada estudo, e eventuais divergências foram resolvidas por meio de debate.

A busca inicial foi realizada no Google Acadêmico, em conjunto, utilizou-se outras fontes como: IEEE Explorer e Elsevier. Na seleção, títulos e resumos foram avaliados para verificar a adequação aos objetivos da pesquisa, excluindo artigos não pertinentes. Na elegibilidade, os artigos foram analisados detalhadamente quanto à qualidade dos métodos e resultados. Os estudos que passaram todas as etapas foram incluídos na revisão sistemática para síntese qualitativa e quantitativa.

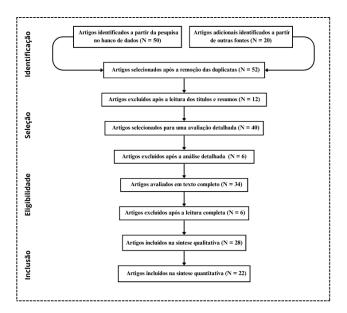

A metodologia de seleção foi baseada no diagrama de fluxo PRISMA proposto por Moher et al. (2009), assegu-

Figura 2: Fluxograma das etapas da pesquisa

rando a replicabilidade e integridade da pesquisa científica. O mesmo pode ser visto na Figura 2.

Foram selecionadas um total de 28 publicações, das quais 22 foram incluídas na análise quantitativa da pesquisa. Todos os estudos são publicações de revistas renomadas, como IEEE, Nature Electronics, Frontiers in Neuroscience, entre outras.

#### 3.2 Descrição das análises realizadas

Inicialmente, recorreu-se à análise de correlação para investigar as interações entre variáveis, com o objetivo de identificar padrões e associações estatisticamente relevantes. Além disso, análises adicionais foram realizadas para avaliar comparativamente esses chips neuromórficos. Para relizar todas as análises foram utilizados os softwares Python e Matlab (Python Software, 2020; MathWorks, 2022).

A correlação de Pearson foi usada para investigar relações lineares entre variáveis, calculando o coeficiente de correlação com a fórmula (Puth et al., 2014):

$$r = \frac{1}{n-1} \sum \left( \frac{x_i - \overline{x}}{s_x} \right) \left( \frac{y_i - \overline{y}}{s_y} \right) \tag{1}$$

Em que:

- r é o coeficiente de correlação de Pearson.

- n é o número de pares de dados.

- $x_i$  e  $y_i$  são os valores individuais das variáveis x e y.

- $\bar{x}$  e  $\bar{y}$  são as médias dos valores de x e y.

- $s_x$  e  $s_y$  são os desvios padrão das variáveis x e y.

- $\frac{x_i \bar{x}}{s_x}$  é o desvio padrão normalizado de  $x_i$ .

- $\frac{y_i \bar{y}}{s_{in}}$  é o desvio padrão normalizado de  $y_i$ .

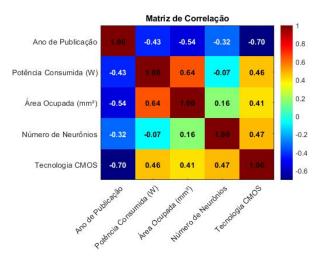

Figura 3: Matriz de correlação entre parâmetros dos chips

Este método computa um coeficiente que varia entre -1 e 1. Em que, -1 representa uma correlação negativa perfeita, indicando uma relação inversa entre as variáveis isto é, quando uma aumenta, a outra diminui. Contrariamente, um coeficiente de +1 indica uma correlação positiva perfeita, em que as variáveis se movem conjuntamente em uma relação direta (Puth et al., 2014).

#### Resultados e Discussões

Para a realização das análises foi construída a Tabela 1, com o intuito de compilar e analisar os dados essenciais que definem as tendências emergentes no campo dos sistemas neuromórficos, envolvendo SNNs e NoCs. Esta tabela serve como um recurso para sintetizar informações extraídas das publicações, facilitando a comparação e análise entre os diversos estudos.

Algumas limitações foram enfretadas, alguns autores apresentaram informações em unidades de medida e formatos diferentes do esperado, o que dificultou a normalização e a comparação direta. Além disso, a omissão de detalhes sobre o número total de neurônios utilizados e os procedimentos de implementação adotados comprometeu uma compreensão mais aprofundada das características de cada projeto. Nos casos em que informações como o número de neurônios no chip não foram fornecidas, esses dados foram ignorados nas análises, evitando distorções decorrentes de suposições ou estimativas arbitrárias.

#### 4.1 Análise da matriz de correlação

Foi contruída uma matriz de correlação com base nos dados apresentados na Tabela 1. Explorou-se as relações entre variáveis como ano da publicação, tecnologia CMOS, área ocupada, potência consumida e número de neurônios. Em vista disso, obteve-se a matriz de correlação representada na Figura 3

A análise das correlações entre o ano de publicação e as outras características dos chips neuromórficos sugere um foco crescente na eficiência energética e na otimiza-

Tabela 1: Síntese dos dados dos artigos selecionados (ordem cronológica)

| Projeto (Autores, Ano)                | SNN      | Circuito  | Neurônios | Potência    | Área                  | CMOS   | NoC       |

|---------------------------------------|----------|-----------|-----------|-------------|-----------------------|--------|-----------|

| BrainScaleS de Schemmel et al. (2010) | IF exp.  | Analógico | 512       | 1000 W      | 430 mm <sup>2</sup>   | 180 nm | _         |

| Carrillo et al. (2012)                | _        | Digital   | 400       | 13.16 mW    | 0.587 mm <sup>2</sup> | 65 nm  | Híbrida   |

| Neurogrid de Choudhary et al. (2012)  | IF quad. | Analógico | 65.536    | 5 W         | 168 mm²               | 180 nm | Estrela   |

| Embrace de Pande et al. (2013)        | IF       | Analógico | 400       | 13.16 mW    | 0.587 mm <sup>2</sup> | 65 nm  | Híbrida   |

| SpiNNaker de Furber et al. (2013)     | IZHI     | Digital   | 1000      | 1 W         | 102 mm²               | 130 nm | Torus 2D  |

| TrueNorth de Akopyan et al. (2015)    | LIF      | Digital   | 256       | 65 mW       | 430 mm <sup>2</sup>   | 28 nm  | Malha 2D  |

| Rolls de Qiao et al. (2015)           | IF exp.  | Analógico | 256       | 4 mW        | 51.4 mm²              | 180 nm | _         |

| Holanda et al. (2016)                 | IZHI     | Digital   | 256       | 147 mW      | 0.23 mm <sup>2</sup>  | 65 nm  | Híbrida   |

| Loihi de Davies et al. (2018)         | LIF      | Digital   | 1024      | _           | $60  \mathrm{mm}^2$   | 14 nm  | Malha 2D  |

| Chen et al. (2019)                    | LIF      | Digital   | 64        | 3.8 pJ/SOP  | 1.72 mm²              | 10 nm  | _         |

| Fan et al. (2019)                     | LIF      | Digital   | 1024      | 2.76E-08 J  | _                     | _      | Malha 2D  |

| Morph IC de Frenkel et al. (2019)     | LIF      | Digital   | 512       | 30 pJ/SOP   | 2.86 mm <sup>2</sup>  | 65 nm  | Híbrida   |

| Vu e Abdallah (2019)                  | _        | Digital   | _         | 1.666 mW    | 0.031 mm²             | 45 nm  | Malha 3D  |

| Vu, Ikechukwu e Ben Abdallah (2019)   | LIF      | Digital   | _         | _           | _                     | 45 nm  | Malha 3D  |

| Vu, Murakami e Abdallah (2019)        | _        | Digital   | _         | 35.96 mW    | 0.365 mm²             | 45 nm  | Malha 3D  |

| Tianjic de Deng et al. (2020)         | _        | Digital   | 256       | _           | _                     | 28 nm  | Malha 2D  |

| Ogbodo et al. (2020)                  | LIF      | Digital   | 256       | 493.5018 mW | 0.12 mm <sup>2</sup>  | 45 nm  | Malha 3D  |

| Jash et al. (2020)                    | IZHI     | Digital   | 16        | 116.86 mW   | 1.61 mm <sup>2</sup>  | 28 nm  | Malha 3D  |

| Javed et al. (2020)                   | LIF      | Digital   | _         | _           | _                     | _      | Malha 2D  |

| Shenjing de Wang et al. (2020)        | _        | Digital   | 256       | 1.26 mW     | 0.49 mm²              | 28 nm  | Malha 2D  |

| Nash de Ikechukwu et al. (2021)       | LIF      | Digital   | 256       | 1.321 mW    | 1.321 mm²             | 45 nm  | Malha 3D  |

| Raine de Fang et al. (2023)           | LIF      | Digital   | 16        | 510 µW      | 0.738 mm²             | 40 nm  | Adaptável |

ção da arquitetura desses dispositivos ao longo do tempo. A correlação negativa moderada com a potência consumida (-0,43) indica que os chips estão se tornando mais eficientes energeticamente. Similarmente, a correlação negativa moderada com o número de neurônios (-0,32) sugere uma possível redução no número de neurônios em prol da eficiência, apontando para mudanças nas estratégias de modelagem e otimização da aestrutura. Além disso, a correlação negativa moderada com a área ocupada pelos chips (-0,54) indica uma tendência de redução no tamanho dos chips, atribuída a avanços na arquitetura e na eficiência de integração, permitindo a incorporação de funcionalidades mais complexas em espaços menores. A correlação negativa forte com a tecnologia CMOS (-0,70) reflete a miniaturização contínua dos componentes dos chips, essencial para aumentar a eficiência, a velocidade e a densidade de transistores, melhorando o desempenho energético e operacional.

Uma correlação positiva e robusta foi identificada entre a área e potência consumida dos chips (0,64), indicando que chips de maior área tendem a consumir mais energia. Esse incremento no consumo é frequentemente atribuído à complexidade acentuada dos circuitos e à capacidade de incorporar funcionalidades adicionais em espaços ampliados. Paralelamente, observa-se uma correlação negativa, ainda que fraca, entre o consumo de energia e o número de neurônios nos chips (-0,07). Este fenômeno sugere que uma maior quantidade de neurônios não necessariamente resulta em um aumento proporcional no consumo de energia, o que pode refletir uma eficiência energética diferenciada, dependendo da configuração neuronal específica. Tal padrão destaca a possibilidade de otimizações na estrutura dos chips que equilibram capacidade computacional e consumo energético. Contudo, dada a fraqueza dessa correlação, não se pode afirmar com certeza que se trata de uma tendência consolidada.

Identifica-se uma correlação positiva moderada entre o consumo de energia e a adoção de tecnologias CMOS (0,46), sugerindo que tecnologias mais avançadas tendem a consumir menos energia. Esta relação destaca que avanços em eficiência energética proporcionados por inovações em tecnologia CMOS são fundamentais para o desenvolvimento de chips mais sustentáveis e de alto desempenho. Adicionalmente, foi identificada uma correlação positiva fraca entre o número de neurônios e a área ocupada pelos chips (0,16). Essa associação implica que chips com maior número de neurônios geralmente exigem mais espaço. No entanto, devido à fraqueza da correlação, esta observação não estabelece necessariamente uma tendência consistente.

É possível notar uma correlação positiva moderada entre a área ocupada pelos chips e o uso de tecnologias CMOS avançadas (0,41), indicando que chips que empregam tecnologias CMOS mais recentes tendem a ocupar áreas menores. Essa redução no tamanho pode ser atribuída aos avanços dessas tecnologias, que permitem maior densidade de componentes em espaços reduzidos, otimizando assim a eficiência da arquitetura e a integração de circuitos. Adicionalmente, identifica-se uma correlação positiva moderada entre o número de neurônios e a evolução da tecnologia CMOS (0,47). Esta relação sugere que o avanço na tecnologia CMOS pode estar associado a uma diminuição no número de neurônios por chip. Essa tendência pode ser explicada pelo aumento da eficiência e da capacidade de processamento dos neurônios individuais. À medida que a tecnologia CMOS avança, os neurônios implementados podem ser capazes de realizar mais funções de maneira eficaz, reduzindo a necessidade de um número elevado de neurônios.

Portanto, fica evidente que os dados apontam para uma evolução consistente dos sistemas neuromórficos, focando muito no aumento da capacidade de processamento, e tam-

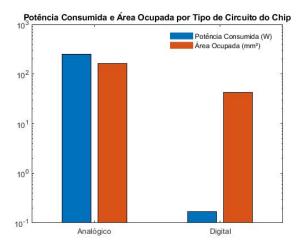

Figura 4: Gráfico do comparativo entre diferentes tipos de circuitos dos chips

bém na melhoria da eficiência energética e na economia de espaço. Essas tendências estão alinhadas com os objetivos de miniaturização e eficiência energética, fundamentais para o progresso da microeletrônica e engenharia de semicondutores. No entanto, é importante notar que, embora as correlações forneçam algumas percepções interessantes, elas não estabelecem relações causais. Por exemplo, uma correlação entre o número de neurônios e o consumo de energia não implica que um maior número de neurônios cause diretamente um aumento no consumo; fatores como a eficiência da arquitetura do circuito também influenciam. Além disso, limitações físicas, custos de fabricação e desafios estruturais podem impactar a integração de neurônios nos chips, destacando a complexidade das decisões estruturais em semicondutores avançados e destaca a importância de uma abordagem equilibrada e bem-informada no desenvolvimento de chips neuromórficos para otimizar performance e eficiência energética.

#### Análise comparativa entre os tipos de circui-4.2

Essa análise foi realizada para identificar o impacto no consumo energético e na área ocupada pelo chip, adontandose as diferentes abordagens de circuitos: analógica e digital. Os dados da Tabela 1 geraram os seguintes resultados que podem ser visualizados na Figura 4. Além disso, as vantangens e desvantagens dos diferentes tipos de circuitos citados nas publicações foram sintetizadas na Tabela 2.

Os circuitos analógicos são eficazes na simulação da dinâmica dos neurônios biológicos por operarem com fluxos contínuos de corrente ou tensão, emulando a natureza analógica da computação cerebral. Eles são apontados como energeticamente eficientes, pois não necessitam de conversão binária de dados. No entanto, está análise indicou que os chips analógicos consomem mais energia e ocupam mais espaço em comparação aos digitais. Isso pode ser devido ao número limitado de amostras desse tipo analisadas ou ainda, devido a variações específicas de arquitetura nos

**Figura 5:** Gráfico do comparativo entre diferentes modelos de neurônios

chips.

Os circuitos digitais foram predominantes na análise, devido à facilidade de fabricação, escalabilidade e integração com tecnologias de semicondutores. Eles demonstram menor consumo de energia e ocupam menos espaço. A lógica binária facilita a integração tecnológica e oferece benefícios como escalabilidade na fabricação e robustez contra variações nos processos de fabricação, essenciais para a produção em larga escala.

É importante destacar o potencial dos circuitos híbridos, que combinando elementos analógicos e digitais, buscam equilibrar a eficiência energética dos componentes analógicos com a precisão dos digitais. Essas estruturas híbridas melhoram a eficiência energética e a simulação do processamento neural. Chips neuromórficos híbridos utilizam circuitos analógicos para simular neurônios e sinapses, e digitais para controle e comunicação, aprimorando a escalabilidade, robustez e eficiência da comunicação interna. Essa abordagem torna os chips neuromórficos adequados para aplicações complexas, como inteligência artificial avançada e sistemas de aprendizado profundo.

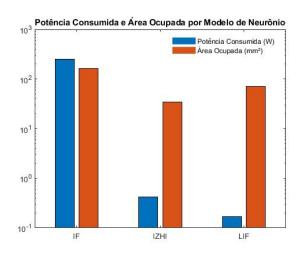

# 4.3 Análise comparativa entre os modelos de neurônios

Essa análise foi realizada para identificar o impacto no consumo energético e na área ocupada pelo chip, adontandose os diferentes modelos de neurônios pulsantes: IF, LIF e IZHI. Os dados da Tabela 1 geraram os seguintes resultados que podem ser visualizados na Figura 5 . Além disso, as vantangens e desvantagens desses modelos citados nas publicações foram sintetizadas na Tabela 3.

Cada modelo de neurônio apresenta diferentes perfis de consumo de energia e ocupação de espaço, importantes para implementações específicas. O modelo IF, embora geralmente considerado o mais simples e eficiente, mostrou um consumo de energia e uma área ocupada maiores do que os modelos IZHI e LIF, possivelmente devido à quantidade limitada de implementações analisadas e variações

Tabela 2. Comparação das características de diferentes tipos de circuito no Chip

| Tipos de Circuito | Vantagens                                                                                                                                                                                                                                                                                             | Desvantagens                                                                                                                                                                                                                                                                                                              |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Digital           |                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                           |

|                   | <ul> <li>Fácil integração com semicondutores existentes.</li> <li>Produção em massa facilitada.</li> <li>Alta confiabilidade e estabilidade.</li> <li>Manutenção simplificada.</li> <li>Baixo custo de produção.</li> </ul>                                                                           | <ul> <li>Incapacidade de capturar dinâmicas neurais contínuas.</li> <li>Limitações na modelagem de comportamentos naturais.</li> <li>Latências devido a conversões analógico-digitais.</li> <li>Dificuldade em simular interações neuronais dinâmicas.</li> <li>Obsolescência rápida com avanços tecnológicos.</li> </ul> |

| Analógico         |                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                           |

|                   | <ul> <li>Alta fidelidade nas dinâmicas neurais.</li> <li>Simulação de propriedades biofísicas complexas.</li> <li>Respostas rápidas e processamento em tempo real.</li> <li>Menos dependente de energia para operações simples.</li> <li>Potencial para interfaces com tecidos biológicos.</li> </ul> | <ul> <li>Maior consumo de energia em operações complexas</li> <li>Maior custo e complexidade de fabricação.</li> <li>Sensível a ruído e variações térmicas.</li> <li>Dificuldade na calibração precisa.</li> <li>Desafios na integração com sistemas digitais.</li> </ul>                                                 |

| Híbrido           |                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                           |

|                   | <ul> <li>Combina precisão digital com naturalidade analógica.</li> <li>Versatilidade para diversas necessidades computacionais.</li> <li>Adaptação a mudanças de requisitos.</li> <li>Equilíbrio entre consumo energético e capacidade.</li> <li>Fomenta inovações tecnológicas.</li> </ul>           | <ul> <li>Complexidade estrutural e custo de desenvolvimento</li> <li>Necessidade de otimizar dois paradigmas de processamento.</li> <li>Riscos na integração de componentes diferentes.</li> <li>Potenciais conflitos de arquiteturas.</li> <li>Custo e esforço adicionais em testes e validação.</li> </ul>              |

|                   | Tabela 3: Comparação das características de di                                                                                                                                                                                                                                                        | erentes modelos de neurônios                                                                                                                                                                                                                                                                                              |

| Modelo de Neurôni |                                                                                                                                                                                                                                                                                                       | Desvantagens                                                                                                                                                                                                                                                                                                              |

| IF                | <ul><li>Simplicidade estrutural.</li><li>Alta eficiência computacional.</li><li>Baixo custo energético.</li></ul>                                                                                                                                                                                     | <ul> <li>Não captura dinâmicas complexas.</li> <li>Modelagem temporal imprecisa.</li> <li>Limitações na plasticidade sináptica.</li> </ul>                                                                                                                                                                                |

| IZHI              | <ul><li>Replicação de padrões biológicos.</li><li>Ideal para simulações avançadas.</li><li>Flexibilidade nos parâmetros.</li></ul>                                                                                                                                                                    | <ul><li>Complexidade na calibração.</li><li>Maior demanda de processamento.</li><li>Alto custo computacional.</li></ul>                                                                                                                                                                                                   |

| LIF               | Bom equilíbrio precisão/eficiência.                                                                                                                                                                                                                                                                   | Menos dinâmicas complexas.                                                                                                                                                                                                                                                                                                |

do modelo IF que introduzem complexidades adicionais.

Usado em estudos escaláveis.

· Ampla literatura de apoio.

O modelo IZHI destacou-se por sua eficiência energética e baixa ocupação de área, conseguindo reproduzir diversas dinâmicas neuronais com uma estrutura compacta. Esse desempenho pode ser atribuído a otimizações específicas que maximizam sua eficiência, tornando-o adequado para aplicações que exigem alta fidelidade biológica sem comprometer a eficiência.

O modelo LIF foi o mais eficiente entre os analisados, com menor consumo de energia e ocupação de área moderada. Ele adiciona um termo de vazamento ao modelo IF, aproximando-se mais da dinâmica neuronal real sem a complexidade adicional. Sua simplicidade e capacidade de capturar comportamentos neuronais essenciais o tornam ideal para implementações em larga escala onde a eficiência energética é fundamental.

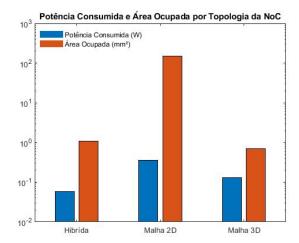

#### 4.4 Análise comparativa entre as topologias de **NoCs**

Limitações na plasticidade sináptica.

Fidelidade limitada em estudos avançados.

Essa análise foi realizada para identificar o impacto no consumo energético e na área ocupada pelo chip, adontandose diferentes topologias de NoCs: Malha 2D, Malha 3D e Híbridas. Os dados da Tabela 1 geraram os seguintes resultados que podem ser visualizados na Figura 6. Além disso, as vantangens e desvantagens dessas topologias citadas nas publicações foram sintetizadas na Tabela 4.

As diferentes topologias em sistemas neuromórficos apresentam características específicas em termos de consumo de energia e ocupação de espaço, adequando-se a diversas necessidades de projetos. A topologia Híbrida se destaca por seu baixo consumo de energia e ocupação mínima de espaço, tornando-se ideal para sistemas que exigem integração flexível de diferentes tecnologias em espaços limitados. Essa topologia é preferida em projetos

Topologia NoC Vantagens Desvantagens Malha<sub>2D</sub> Fácil implementação e manutenção. Aumento de latência com o crescimento. Escalabilidade eficaz. Limitações de largura de banda. Suscetível a congestionamentos. Custo de fabricação efetivo. Estrela Baixa latência com o nó central. Ponto único de falha. Configuração simples. · Escalabilidade limitada. Conexões locais diretas. Dependência do nó central. Torus 2D · Roteamento complexo. · Múltiplos caminhos redundantes. Latência maior em distâncias longas. Distribuição uniforme de carga. Flexibilidade limitada. Alta tolerância a falhas. Malha 3D · Reduz latência. Gestão térmica desafiadora. · Alta densidade de conexões. Alto custo de fabricação e manutenção. Melhor desempenho de processamento. Dificuldade de integração em múltiplas camadas. Híbrida · Estrutura complexa. Flexível para cargas específicas. Altos custos de desenvolvimento e teste. · Otimiza tráfego e eficiência energética. · Integra redes complexas. Desafios em balancear desempenho e eficiência. Adaptável Implementação complexa. · Reconfiguração dinâmica conforme o tráfego. Alto overhead de reconfiguração. Otimiza a largura de banda.

Tabela 4: Comparação das características de diferentes topologias NoCs

· Reduz congestionamento.

Figura 6: Gráfico do comparativo entre diferentes topologias de redes-em-chip

que beneficiam de uma abordagem multifuncional, combinando o melhor de diferentes arquiteturas de redes para maximizar a eficiência e adaptabilidade.

Por outro lado, a topologia de Malha 2D, apesar de apresentar um consumo de energia elevado e grande ocupação de espaço, é valorizada por sua simplicidade de implementação e baixo custo. Sua popularidade em diversos projetos indica uma preferência por soluções onde a simplicidade e o custo são mais críticos do que a eficiência de espaço e energia. Essa topologia é frequentemente adotada em projetos onde a densidade de componentes não é uma restrição importante, facilitando sua implementação em larga escala.

A topologia de Malha 3D oferece um equilíbrio entre consumo de energia e uso eficiente do espaço, sendo preferida para aplicações que demandam alta densidade de interconexões e processamento rápido. Utilizada em diversos projetos avançados, essa topologia reflete a busca por soluções que maximizem a capacidade de processamento e a compactação de circuitos. Ideal para tecnologias que necessitam de altas taxas de transferência de dados e mínima latência, a Malha 3D é indicada para aplicações de ponta que exigem o máximo desempenho em espaços extremamente confinados. Além disso, a análise demonstrou que a topologia de Malha 3D foi citada em 8 dos 22 estudos, evidenciando sua predominância no cenário atual, sobretudo quando combinada com a Malha 2D, as quais juntas dominam as implementações modernas em publicações de 2019 e 2020.

· Maior consumo de recursos.

#### 4.5 Desafios das implementações neuromórficas

As SNNS enfrentam desafios consideráveis ao serem implementadas em dispositivos de hardware, especialmente quando interconectadas por NoCs. A implementação em hardware exige um profundo entendimento das características de funcionamento das SNNs, e também uma habilidade especializada para adaptar suas funcionalidades em um ambiente que pode restringir sua operação ótima. Nesse contexto, alguns dos principais desafios foram sintetizados a partir dos estudos selecionados (Basu et al., 2022; Chen et al., 2022; Lobo et al., 2020; Walter et al., 2015):

- · Complexidade em replicar dinâmicas sinápticas precisas com adaptabilidade em tempo real;

- Consumo de energia e gestão térmica nos chips;

- Escalabilidade e performance com aumento de neurônios e sinapses;

- Desenvolvimento de algoritmos de aprendizado eficazes em SNNs;

- Controle de fluxo de dados para evitar congestionamentos na NoC.

## 4.6 Avanços nas implementações neuromórficas

Um dos mecanismos de plasticidade mais utilizados em projetos é o STDP, porém, ajustar a condutância das sinapses em chips é um desafio. Gupta e Saurabh (2023) apresentam uma solução para otimizar o aprendizado não supervisionado em SNNs, usando um dispositivo MOSFET (Ge-FD-SOI) com gates assimétricos. Este dispositivo requer menos transistores e oferece menor latência. Os gates assimétricos permitem um controle preciso da condutância das sinapses, facilitando a gestão da corrente com base na correlação temporal dos disparos neurais, conforme a regra STDP. A configuração envolve dois gates de tamanhos diferentes no transistor, proporcionando uma regulação eficiente da atividade elétrica, essencial para simular o comportamento neuronal de maneira precisa e com menor consumo de energia. O dispositivo melhora a eficiência energética e a compactação do hardware, e ao ser integrado em um sistema, reconheceu dígitos manuscritos do conjunto MNIST com 84% de precisão.

Im et al. (2022) discutem a complexidade dos métodos de aprendizado em SNNs e os desafios de implementá-los eficientemente em hardware neuromórfico. Eles propõem a codificação chamade de Time-to-First-Spike (TTFS), que simplifica os algoritmos de aprendizado, reduzindo a complexidade computacional e o número de pulsos necessários para transmissão de informações. A técnica converte a intensidade de cada pixel de uma imagem em um único pico, onde o tempo de disparo é inversamente proporcional à intensidade do pixel, permitindo que pixels mais claros disparem mais rapidamente. Isso resulta em uma operação mais eficiente em termos energéticos. A implementação do TTFS em hardware neuromórfico também permite aprendizado diretamente no dispositivo, ajustando os pesos com base na diferença entre o tempo de disparo real e o tempo de disparo alvo de cada neurônio, facilitando um treinamento mais preciso. Este método, aplicado na classificação do conjunto de dados MNIST, alcançou uma precisão de 96%.

Javed et al. (2020) propõem o uso de SNNs para prever congestionamentos em arquiteturas NoCs. Eles desenvolveram um modelo que identifica padrões de congestionamento aproveitando a natureza temporal do tráfego. O modelo opera em dois níveis: no nível do roteador, onde cada um possui sua própria SNN para prever congestionamentos locais, e no nível da rede, com uma única SNN monitorando todo o sistema, o que permitiu prever congestionamentos com até 30 ciclos de clock de antecedência, alcançando uma precisão de até 96,59%, e utilizando nove vezes menos área de hardware em comparação com métodos anteriores. O modelo captura variações temporais nos padrões de tráfego nos roteadores e usa essas informações para treinar as SNNs. No nível do roteador, cada SNN prevê congestionamentos locais com base na ocupação dos buffers de entrada. No nível da rede, uma única SNN recebe dados agregados de todos os roteadores para fazer uma previsão global. Essas previsões possibilitam intervenções proativas para balancear a carga de tráfego e ajustar rotas antes que ocorra congestionamento, melhorando a qualidade do serviço e a eficiência da NoC.

Vu, Murakami e Abdallah (2019) desenvolveram um algoritmo de roteamento multicast inovador para NoCs tridimensionais, focado em aplicações críticas que requerem tolerância a falhas. O algoritmo, chamado Fault-Tolerant k-Means Based Multicast Routing Algorithm (FT-KMCR), minimiza congestionamentos e melhora a latência e a taxa de transmissão de pulsos, mesmo com até 20% de falhas. Usando o método k-means, o FT-KMCR divide a rede em partições equilibradas, configurando uma árvore de multicast com rotas de backup pré-planejadas. Essas rotas são estabelecidas offline e configuradas nas tabelas de roteamento antes da operação em tempo real, permitindo a alternância automática para rotas de backup em caso de falhas, garantindo comunicação contínua.

# Conclusões

Esta pesquisa investigou a integração das SNNs em chips neuromórficos, com foco nas arquiteturas de NoCs para otimizar a comunicação interna e a eficiência energética desses sistemas. Os resultados destacam a importância das topologias de NoC e das estratégias de roteamento na performance dos chips neuromórficos, além do impacto dos modelos de neurônios e das regras de aprendizagem na funcionalidade dos sistemas.

A compilação dos dados apresentados na Tabela 1 demonstrou a existência de diversas abordagens para a implementação de chips neuromórficos. As variações identificadas – que abrangem modelos neurais, tecnologias de fabricação, tipos de circuitos e configurações topológicas – oferecem respostas às duas primeiras perguntas de pesquisa. Em síntese, os dados indicam que algumas estratégias priorizam a simplicidade e o baixo custo, enquanto outras focam na eficiência energética e na miniaturização.

A análise de correlação corroborou essas distinções ao revelar interações importantes na arquitetura dos dispositivos. Observou-se, por exemplo, uma correlação negativa entre o ano de publicação, a potência consumida e a área ocupada, o que indica um foco crescente na eficiência energética e na miniaturização. Além disso, a correlação fraca entre o ano de publicação e o número de neurônios indica uma ênfase na qualidade e eficiência dos neurônios, ao invés de quantidade . Ademais, a forte correlação positiva entre área e potência destaca o impacto da complexidade dos circuitos no consumo de energia.

As análises comparativas ajudaram a responder à terceira pergunta de pesquisa, indicando, por meio dos gráficos, que a combinação de circuitos digitais com o modelo de neurônio LIF e a topologia de Malha 3D é a abordagem mais eficaz para reduzir o consumo energético e diminuir o tamanho dos chips – aspectos que se destacam como tendências emergentes nas pesquisas. Entretanto, os principais desafios ainda residem na complexidade dos algoritmos de roteamento e nos métodos de aprendizagem dos neurônios.

Portanto, fica evidente que esses chips prometem um avanço importante na simulação de processos neurais biológicos, levando a uma nova era de dispositivos eletrônicos que podem aprender e adaptar-se de maneira similar

ao cérebro humano. A capacidade de processar informações de forma eficiente e em larga escala torna os chips neuromórficos uma tecnologia essencial para o futuro da computação e da inovação tecnológica.

## Agradecimentos

Agradecemos ao CNPq pelo apoio financeiro ao desenvolvimento deste trabalho.

#### Referências

- Ahmad, K. e Sethi, M. A. J. (2020). Review of network on chip routing algorithms, EAI Endorsed Transactions on Context-aware Systems and Applications 7(22). Disponível em: https://doi.org/10.4108/eai.23-12-2020.16

- Akopyan, F., Sawada, J., Cassidy, A., Alvarez-Icaza, R., Arthur, J., Merolla, P., Imam, N., Nakamura, Y., Datta, P., Nam, G.-J., Taba, B., Beakes, M., Brezzo, B., Kuang, J. B., Manohar, R., Risk, W. P., Jackson, B. e Modha, D. S. (2015). Truenorth: Design and tool flow of a 65 mw 1 million neuron programmable neurosynaptic chip, IEEE Transactions on Computer-Aided Design of Integrated Cir*cuits and Systems* **34**(10): 1537–1557. Disponível em: https://doi.org/10.1109/TCAD.2015.2474396.

- Alimi, I. A., Patel, R. K., Aboderin, O., Abdalla, A. M., Gbadamosi, R. A., Muga, N. J., Pinto, A. N. e Teixeira, A. L. (2021). Network-on-chip topologies: Potentials, technical challenges, recent advances and research direction, in I. A. Alimi, O. Aboderin, N. J. Muga e A. L. Teixeira (eds), Network-on-Chip, IntechOpen, Rijeka, chapter 3. Disponível em: https://doi.org/10.5772/intechopen.97262.

- Basu, A., Deng, L., Frenkel, C. e Zhang, X. (2022). Spiking neural network integrated circuits: A review of trends and future directions, 2022 IEEE Custom Integrated Circuits Conference (CICC), pp. 1–8. Disponível em: https://doi.org/10.1109/CICC53496.2022.9772783.

- Carrillo, S., Harkin, J., McDaid, L., Pande, S., Cawley, S., McGinley, B. e Morgan, F. (2012). Hierarchical networkon-chip and traffic compression for spiking neural network implementations, 2012 IEEE/ACM Sixth International Symposium on Networks-on-Chip, pp. 83-90. Disponível em: https://doi.org/10.1109/NOCS.2012.17.

- Chen, G. K., Kumar, R., Sumbul, H. E., Knag, P. C. e Krishnamurthy, R. K. (2019). A 4096-neuron 1m-synapse 3.8-pj/sop spiking neural network with on-chip stdp learning and sparse weights in 10-nm finfet cmos, IEEE Journal of Solid-State Circuits 54(4): 992-1002. Disponível em: https://doi.org/10.1109/JSSC.2018.2884901.

- Chen, L., Xiong, X. e Liu, J. (2022). A survey of intelligent chip design research based on spiking neural networks, IEEE Access 10: 89663-89686. Disponível em: https: //doi.org/10.1109/ACCESS.2022.3200454.

- Choudhary, S., Sloan, S., Fok, S., Neckar, A., Trautmann, E., Gao, P., Stewart, T., Eliasmith, C. e Boahen, K. (2012). Silicon neurons that compute, in A. E. P. Villa,

- W. Duch, P. Érdi, F. Masulli e G. Palm (eds), Artificial Neural Networks and Machine Learning – ICANN 2012, Springer Berlin Heidelberg, Berlin, Heidelberg, pp. 121–128. Disponível em: https://doi.org/10.1007/978-3-642-3 3269-2\_16.

- Davies, M., Srinivasa, N., Lin, T.-H., Chinya, G., Cao, Y., Choday, S. H., Dimou, G., Joshi, P., Imam, N., Jain, S., Liao, Y., Lin, C.-K., Lines, A., Liu, R., Mathaikutty, D., McCoy, S., Paul, A., Tse, J., Venkataramanan, G., Weng, Y.-H., Wild, A., Yang, Y. e Wang, H. (2018). Loihi: A neuromorphic manycore processor with on-chip learning, IEEE Micro 38(1): 82-99. Disponível em: https: //doi.org/10.1109/MM.2018.112130359.

- Deng, L., Wang, G., Li, G., Li, S., Liang, L., Zhu, M., Wu, Y., Yang, Z., Zou, Z., Pei, J., Wu, Z., Hu, X., Ding, Y., He, W., Xie, Y. e Shi, L. (2020). Tianjic: A unified and scalable chip bridging spike-based and continuous neural computation, IEEE Journal of Solid-State Circuits 55(8): 2228-2246. Disponível em: https://doi.org/10.1109/JSSC.2 020.2970709.

- Fan, Y., Zou, C., Liu, K., Kuang, Y. e Cui, X. (2019). A digital neuromorphic hardware for spiking neural network, 2019 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), pp. 1-2. Disponível em: ht tps://doi.org/10.1109/EDSSC.2019.8754093.

- Fang, C., Wang, C., Zhao, S., Tian, F., Yang, J. e Sawan, M. (2023). A 510  $\mu$ w 0.738-mm<sup>2</sup> 6.2-pj/sop online learning multi-topology snn processor with unified computation engine in 40-nm cmos, IEEE Transactions on Biomedical Circuits and Systems 17(3): 507-520. Disponível em: ht tps://doi.org/10.1109/TBCAS.2023.3279367.

- Frenkel, C., Legat, J.-D. e Bol, D. (2019). A 65-nm 738ksynapse/mm2 quad-core binary-weight digital neuromorphic processor with stochastic spike-driven online learning, 2019 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1-5. Disponível em: https: //doi.org/10.1109/ISCAS.2019.8702793.

- Furber, S. B., Lester, D. R., Plana, L. A., Garside, J. D., Painkras, E., Temple, S. e Brown, A. D. (2013). Overview of the spinnaker system architecture, IEEE Transactions on Computers **62**(12): 2454–2467. Disponível em: https://doi.org/10.1109/TC.2012.142.

- Gupta, A. e Saurabh, S. (2023). On-chip unsupervised learning using stdp in a spiking neural network, IEEE Transactions on Nanotechnology 22: 365–376. Disponível em: https://doi.org/10.1109/TNANO.2023.3293011.

- Holanda, P. C., Reinbrecht, C. R. W., Bontorin, G., Bandeira, V. V. e Reis, R. A. L. (2016). Dhyana: A noc-based neural network hardware architecture, 2016 IEEE International Conference on Electronics, Circuits and Systems (ICECS), pp. 177–180. Disponível em: https://doi.org/10.1109/ ICECS.2016.7841161.

- Ikechukwu, O. M., Dang, K. N. e Abdallah, A. B. (2021). On the design of a fault-tolerant scalable three dimensional noc-based digital neuromorphic system with on-chip learning, IEEE Access 9: 64331–64345. Disponível em: https://doi.org/10.1109/ACCESS.2021.3071089.

- Im, J., Kim, J., Yoo, H.-N., Baek, J.-W., Kwon, D., Oh, S., Kim, J., Hwang, J., Park, B.-G. e Lee, J.-H. (2022). Onchip trainable spiking neural networks using time-tofirst-spike encoding, IEEE Access 10: 31263-31272. Disponível em: https://doi.org/10.1109/ACCESS.2022.31

- Jaeger, R. C. e Blalock, T. N. (2015). Microelectronic Circuit Design, 5th edn, McGraw-Hill Education, New York.

- Jash, A., Ghosh, A., Noyel, N., Patra, R. e Mondal, H. K. (2020). 3d-nocnn: Noc based clustered architecture for neural networks, 2020 24th International Symposium on *VLSI Design and Test (VDAT)*, pp. 1–4. Disponível em: https://doi.org/10.1109/VDAT50263.2020.9190590.

- Javed, A., Harkin, J., McDaid, L. e Liu, J. (2020). Exploring spiking neural networks for prediction of traffic congestion in networks-on-chip, 2020 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–5. Disponível em: https://doi.org/10.1109/ISCAS45731.202 0.9180630.

- Kundu, S. e Chattopadhyay, S. (2014). Network-on-chip: the next generation of system-on-chip integration, Taylor & Francis. Disponível em: https://doi.org/10.1201/97 81315216072.

- Lobo, J. L., Del Ser, J., Bifet, A. e Kasabov, N. (2020). Spiking neural networks and online learning: An overview and perspectives, Neural Networks 121: 88–100. Disponível em: https://doi.org/10.1016/j.neunet.2019.09.004.

- MathWorks, T. (2022). Matlab version: 9.13.0 (r2022b). Disponível em: https://www.mathworks.com.

- Mead, C. (1990). Neuromorphic electronic systems, Proceedings of the IEEE 78(10): 1629-1636. Disponível em: https://doi.org/10.1109/5.58356.

- Moher, D. et al. (2009). Preferred reporting items for systematic reviews and meta-analyses: The prisma statement, *PLoS Medicine* **6**(7): e1000097. Disponível em: https://doi.org/10.1371/journal.pmed.1000097.

- Ogbodo, M., Vu, T., Dang, K. e Abdallah, A. (2020). Lightweight spiking neuron processing core for large-scale 3d-noc based spiking neural network processing systems, 2020 IEEE International Conference on Big Data and *Smart Computing (BigComp)*, pp. 133–139. Disponível em: https://doi.org/10.1109/BigComp48618.2020.00-86.

- Pande, S. et al. (2013). Modular neural tile architecture for compact embedded hardware spiking neural network, *Neural Processing Letters* **38**: 131–153. Disponível em: https://doi.org/10.1007/s11063-012-9274-5.

- Puth, M.-T., Neuhäuser, M. e Ruxton, G. D. (2014). Effective use of pearson's product—moment correlation coefficient, Animal Behaviour 93: 183–189. Disponível em: https://doi.org/10.1016/j.anbehav.2014.05.003.

- Python Software (2020). Python Language Site: Documentation. Disponível em: https://www.python.org/d oc/.

- Qiao, N. et al. (2015). A re-configurable on-line learning spiking neuromorphic processor comprising 256 neurons and 128k synapses, Frontiers in Neuroscience 9: 141. Disponível em: https://doi.org/10.3389/fnins.2015

- Schemmel, J., Brüderle, D., Grübl, A., Hock, M., Meier, K. e Millner, S. (2010). A wafer-scale neuromorphic hardware system for large-scale neural modeling, 2010 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1947–1950. Disponível em: https://doi.org/10.1 109/ISCAS.2010.5536970.

- Schuman, C. D. et al. (2017). A survey of neuromorphic computing and neural networks in hardware. Disponível em: https://doi.org/10.48550/arXiv.1705.06963.

- Vu, T. H. e Abdallah, A. B. (2019). Low-latency k-means based multicast routing algorithm and architecture for three dimensional spiking neuromorphic chips, 2019 IEEE International Conference on Big Data and Smart Computing (BigComp), pp. 1–8. Disponível em: https://doi. org/10.1109/BIGCOMP.2019.8679363.

- Vu, T. H., Ikechukwu, O. M. e Ben Abdallah, A. (2019). Fault-tolerant spike routing algorithm and architecture for three dimensional noc-based neuromorphic systems, IEEE Access 7: 90436–90452. Disponível em: https://doi.org/10.1109/ACCESS.2019.2925085.

- Vu, T. H., Murakami, Y. e Abdallah, A. B. (2019). Graceful fault-tolerant on-chip spike routing algorithm for mesh-based spiking neural networks, 2019 2nd International Conference on Intelligent Autonomous Systems (ICoIAS), pp. 76-80. Disponível em: https://doi.org/ 10.1109/ICoIAS.2019.00020.

- Walter, F., Röhrbein, F. e Knoll, A. (2015). Neuromorphic implementations of neurobiological learning algorithms for spiking neural networks, Neural Networks 72: 152-167. Disponível em: https://doi.org/10.1016/j.neun et.2015.07.004.

- Wang, B., Zhou, J., Wong, W.-F. e Peh, L.-S. (2020). Shenjing: A low power reconfigurable neuromorphic accelerator with partial-sum and spike networks-on-chip. Disponível em: https://doi.org/10.48550/arXiv.1911. 10741.

- Yamazaki, K., Vo-Ho, V.-K., Bulsara, D. e Le, N. (2022). Spiking neural networks and their applications: A review, Brain Sciences 12(7). Disponível em: https://doi. org/10.3390/brainsci12070863.